DAFTAR ISI

1. Soal 1Bicmos [kembali]

2. Soal 2 Bicmos [kembali]

3. Soal 1 IC Multivibrator [kembali]

A.

B.

C.

D.

E.

4. Soal 2 IC Multivibrator [kembali]

Solusi :

Jawaban D

5. Soal 1 A/D Converter [kembali]

6. Soal 2 A/D Converter [kembali]

1. Soal 1Bicmos [kembali]

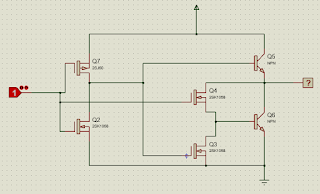

Bagaimana prinsip kerja dari rangkaian diatas apabila keadaan Bicmos seperti diatas ?

A. Arus dari VCC akan mengalir ke emitter Q5 sehingga output berlogika 1

B. Arus dari VCC akan mengalir ke emitter Q5 sehingga output berlogika 0

B. Arus dari VCC akan mengalir ke emitter Q5 sehingga output berlogika 0

C. Arus dari VCC tidak mengalir ke emitter Q5 sehingga output berlogika 1

D. Arus dari VCC tidak mengalir ke emitter Q5 sehingga output berlogika 0

E. Arus dari VCC akan mengalir ke basis Q5 sehingga output berlogika 1

Solusi :

Jawaban : D

Pada saat input berlogika 1, maka pada Q7(p-mosfet) akan OFF sehingga tidak ada arus mengalir ke drain mosfet, dengan begini arus juga tidak mengalir ke basis Q5, karena tidak ada arus mengalir di basis, arus dari tegangan VCC juga tidak bisa mengalir ke emitter Q5, sehingga tidak ada arus yang mengalir di output, yang menandakan bahwa outputnya berlogika 0

2. Soal 2 Bicmos [kembali]

Apa nama dari rangkaian di atas?

A. CMOS Inverter

B. BiCMOS Inverter

C. CMOS NAND

D. BiCMOS NAND

E. BiCMOS AND

Solusi :

Jawaban B

Pada saat input berlogika 1, maka pada Q7(p-mosfet) akan OFF sehingga tidak ada arus mengalir ke drain mosfet, dengan begini arus juga tidak mengalir ke basis Q5, karena tidak ada arus mengalir di basis, arus dari tegangan VCC juga tidak bisa mengalir ke emitter Q5, sehingga tidak ada arus yang mengalir di output, yang menandakan bahwa outputnya berlogika 0

Jawaban B

Pada saat input berlogika 1, maka pada Q7(p-mosfet) akan OFF sehingga tidak ada arus mengalir ke drain mosfet, dengan begini arus juga tidak mengalir ke basis Q5, karena tidak ada arus mengalir di basis, arus dari tegangan VCC juga tidak bisa mengalir ke emitter Q5, sehingga tidak ada arus yang mengalir di output, yang menandakan bahwa outputnya berlogika 0

Pada saat input berlogika 0, maka pada Q7(p-mosfet) akan ON sehingga arus dari tegangan VCC akan mengalir dari source ke drain lalu ke basis Q5, karna ada arus di basis Q5 maka memicu arus mengalir dari tegangan VCC ke kolektor Q5 dan diteruskan ke emitter Q5 lalu arus ini akan menjadi output, jika ada arus yang mengalir maka ini menandakan bahwa outputnya berlogika 1.

Input dan Output yang berlawanan dinamakan inverter. Pada rangkaian terdapat transistor FET dan transistor BJT sehingga dinamakan BiCMOS.

Input dan Output yang berlawanan dinamakan inverter. Pada rangkaian terdapat transistor FET dan transistor BJT sehingga dinamakan BiCMOS.

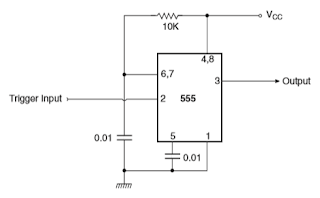

3. Soal 1 IC Multivibrator [kembali]

Bentuk gelombang dari Gambar (b) diterapkan pada terminal RESET dari rangkaian multivibrator astabil dari Gambar (a). Gambarlah gelombang output!

B.

C.

D.

E.

Solusi :

Jawaban A

Jawaban A

Rangkaian yang ditunjukkan pada Gambar (a) adalah multivibrator astabil dengan bentuk gelombang simetris 500 Hz yang diterapkan pada terminal RESET-nya. Terminal RESET bergantian TINGGI dan RENDAH selama 1,0 ms. Ketika input RESET RENDAH, output dipaksa ke status RENDAH. Ketika input RESET TINGGI, bentuk gelombang astabil muncul di output. Periode waktu TINGGI dan RENDAH dari multivibrator astabil ditentukan sebagai berikut:

HIGH time=0.69×14.5×103×0.01×10−6 =100ms

LOW time=0.69×14.5×103×0.01×10−6 =100ms

Output astable adalah bentuk gelombang simetris 5 kHz. Setiap kali terminal RESET pergi ke TINGGI selama 1,0 ms, lima siklus gelombang 5 kHz muncul di output. Gambar diatas menunjukkan bentuk gelombang output yang muncul di terminal 3 IC pengatur waktu.

4. Soal 2 IC Multivibrator [kembali]

Berdasarkan rangkaian multivibrator monostable pada Gambar dibawah. Terminal pemicu (pin 2 dari IC) digerakkan oleh bentuk gelombang simetris 10 kHz. Tentukan frekuensi dan duty cycle gelombang keluaran!

A. Frekuensi = 10kHz, Duty cycle = 0,55

B. Frekuensi = 5kHz, Duty cycle = 0,5

C. Frekuensi = 10kHz, Duty cycle = 0,45

D. Frekuensi = 5kHz, Duty cycle = 0,55

E. Frekuensi = 10kHz, Duty cycle = 0,5

Solusi :

Jawaban D

- Frekuensi dari gelombang pemicu = 10kHz

- Periode waktu antara dua ujung leading atau trailing = 100 µs

- Lebar pulsa yang diharapkan dari output monoshot = 1.1 RC = 1.1 x 104 x 10-8 = 110 µs

- Gelombang pemicu adalah yang simetris dengan periode waktu tinggi dan rendah masing-masing 50 µs. Karena periode waktu keadaan RENDAH dari bentuk gelombang pemicu kurang dari lebar pulsa output yang diharapkan, ia dapat berhasil memicu monoshot pada ujung trailingnya.

- Karena periode waktu antara dua trailing edge berturut-turut adalah 100 µs dan lebar pulsa keluaran yang diharapkan adalah 110 µs, hanya tepi trailing alternatif dari gelombang pemicu yang akan memicu monoshot.

- Frekuensi bentuk gelombang output = 10/2 = 5 kHz.

- Periode gelombang output = 1/(5 x 103) = 200 µs

Oleh karena itu, duty cycle dari gelombang output = 110/200 = 0.55

5. Soal 1 A/D Converter [kembali]

Tentukan rata-rata waktu konversi A/D converter yang di tunjukkan pada gambar 12.32 yang dimana frekuensi kunci sebesar 1MHz

A. 4095 µs

B. 4.095 µs

C. 2047 ms

D. 2.047 ms

E. 2.047 µs

B. 4.095 µs

C. 2047 ms

D. 2.047 ms

E. 2.047 µs

Solusi :

Jawaban C

- Apabila converter A/D memiliki variable yang maksimum ketika tegangan analog input tepat dibawah tegang analog input skala penuh

- Waktu konversi rata” sama dengan setengah waktu waktu konversi biasa yang ditentukan dalam kasus converter tersebut

- Waktu konversi maksimum sama dengan waktu yang diambil oleh 212 − 1 = 4095 siklus input clock.

- Periode waktu clock = 1 / (1 × 106 = 1µs)

- waktu konversi maksimum = 4095 × 1 = 4095µs = 4.095 ms.

- Rata-rata waktu konversi = (4.095 / 2) = 2.047 ms

6. Soal 2 A/D Converter [kembali]

Gambar diatas adalah logica yang akan terjadi ketika A/D Converter di ON kan. Dari gambar diatas berapakah logika yang akan muncul yang ditunjukkan pada tanda A dan B ?

a. 0111 dan 1111

b. 1111 dan 0101

c. 1111 dan 1010

d. 0101 dan 1111

e. 0000 dan 1111

Solusi :

Jawaban B

Karena logika sebelum A adalah 1111 sehingga yang akan muncul 1111 dan 1110. pada B logika sebelumnya adalah 0101 sehingga logika yang dapat terjadi adalah 0101 dan 0100

7. Soal 3 A/D Converter [kembali]

Karena logika sebelum A adalah 1111 sehingga yang akan muncul 1111 dan 1110. pada B logika sebelumnya adalah 0101 sehingga logika yang dapat terjadi adalah 0101 dan 0100

7. Soal 3 A/D Converter [kembali]

Bandingkan penghemat daya

untuk konversi waktu-bit-jenis-konverter A / D dengan konverter A / D-bit-jalan

berturut-turut kurang lebih tipe A / D converter jika keduanya bekerja pada

frekuensi clock 10 MHz.

A. 0,1 µs

B. 0,2 µs

C. 0,4 µs

D. 0,6 µs

E. 0,8 µs

Solusi

Jawaban E

• Periode waktu clock =

0,1 µs.

• Rata-rata waktu

konversi untuk counter type A/D converter diberikan [(28 – 1) / 2] × 0 1 = 12.75

µs.

• Waktu konversi dalam

kasus konverter tipe A / D yang diperkirakan berturut-turut diberikan oleh 8 ×

0,1 = 0,8 µs.

Tidak ada komentar:

Posting Komentar